产品动态

- 群创12.1寸 G121ICE-LM2 对比度1000:1 常

- G270QAN01.4 友达27寸 400 cd/m² 分辨率2

- G190ETT01.1 友达19寸 分辨率1280*1024

- 18.5寸G185HAT01.1 友达 对比度1000:1 分

- 友达G101EAT02.6 10.1寸 分辨率1280*800

- G156HAN02.303 友达15.6寸 对比度1000:1

- G057QAN01.1 友达5.7寸 常黑显示 1000:1

- G238HAN04.0 友达23.8寸 常黑显示 分辨

- 友达8.4寸 G084SAN01.0 常黑显示 分辨

- G057QAN01.0 友达 5.7寸 500 cd/m² 常黑

全国统一服务热线:

15382323032

客服QQ:3234659108

手机:15382323032

地址:浙江省杭州市余杭区五常街道西溪软件园金牛座B2座4层4118-4119

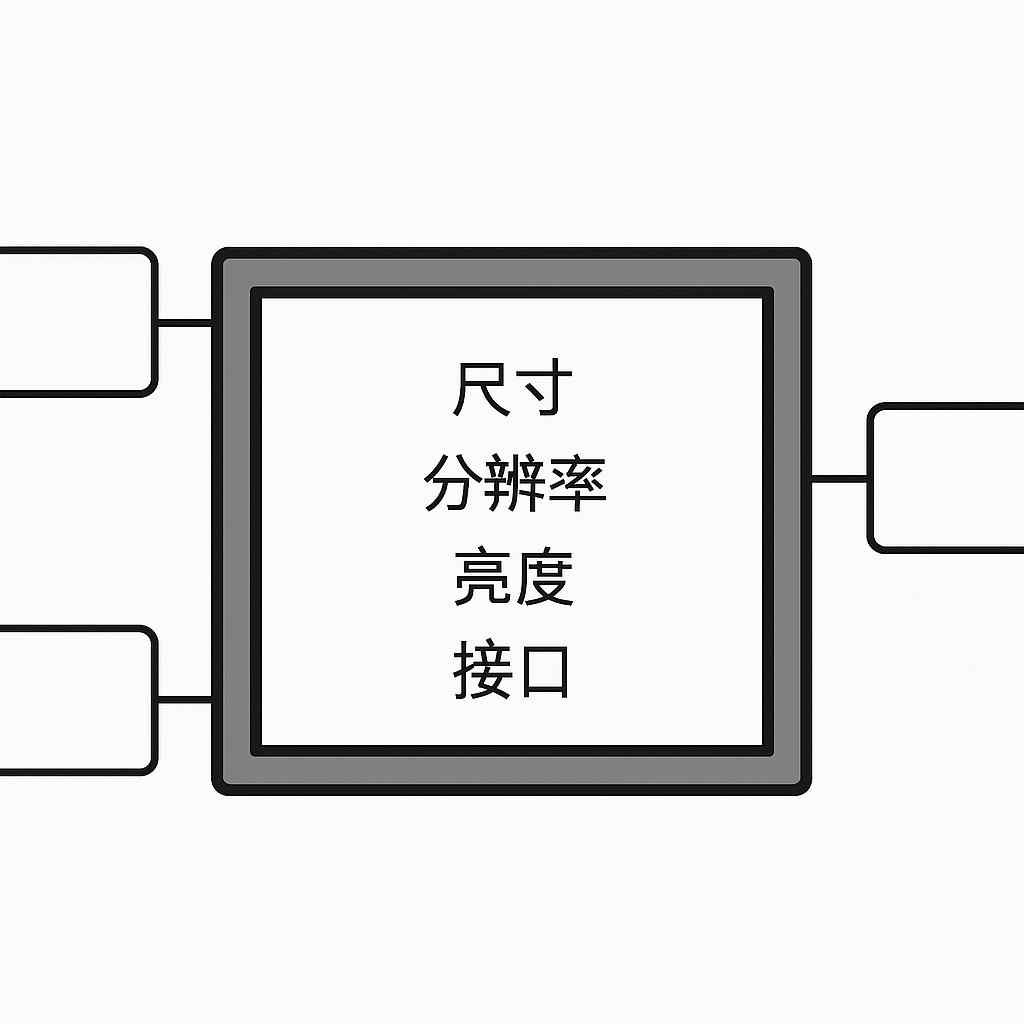

RGB还是LVDS?LCD工业液晶屏幕信号传输选型

在工业设备里做显示,很多项目卡在“信号怎么从主板送到屏上”。同一块液晶屏,换一种传输方式,现场稳定性、EMI整改成本、线束复杂度、甚至后期可维护性都会完全不同。RGB(并行RGB/TTL)与LVDS(面板常用的FPD-Link/OpenLDI一类LVDS链路)看起来都是“把像素送到LCD液晶屏”,但它们的工程属性几乎是两个世界:一个靠多根单端并行线同步像素节拍,另一个靠低摆幅差分对把数据串行化再送过去。

精显从工业应用最关心的维度——抗干扰、线束与连接器、可达带宽、布线难度、成本与维护、以及常见踩坑点——做系统对比,并给出液晶模组在不同场景下的选择建议。

一、“RGB”和“LVDS”到底指什么

1、RGB:并行RGB/TTL

在很多MCU/MPU里,RGB接口本质是并行像素总线:每个像素用若干根数据线同时输出,配合像素时钟与行场同步信号,把像素节拍“喂”给面板的TCON(TimingController)。典型信号包括像素时钟(PIXCLK/LCD_CLK/DOTCLK)、HSYNC、VSYNC、DE(DataEnable),以及RGB数据位(如18位或24位数据线)。NXP的应用笔记在描述LCD面板接口时明确指出面板需要HSYNC、VSYNC、DE、PIXCLK及完整RGB数据线。

ST的LTDC(LCD-TFTDisplayController)介绍文档也说明控制信号(HSYNC、VSYNC、DE)以及像素时钟可配置极性,并用于驱动LCD-TFT显示。

可以把它理解成:RGB是“并行+同步时钟”的裸像素输出,线很多,时序靠主控持续输出。

2、LVDS:面板接口中常说的LVDS

LVDS首先是一套电气标准(TIA/EIA-644/644A定义的低电压差分信号接口)。TI的设计指南提到LVDS相关标准由ANSI/TIA/EIA-644A等规格定义。

在显示行业里,“LVDS屏”往往不是指“任意LVDS差分线”,而是指一种成熟的面板链路(常见被称为FPD-Link/OpenLDI/PanelLink一类):把并行RGB与控制信号序列化后,用若干组差分对(数据对+时钟对)送到液晶模组端再反序列化。典型的单像素24bpp映射是4条LVDS数据对+1条LVDS时钟对(4D+C)。TI的FPD-Link器件资料明确写到“24位RGB+控制信号序列化后通过4data+clock(4D+C)LVDS接口输出”。

可以把它理解成:LVDS在面板场景里经常代表“差分序列化链路”,线更少、摆幅更小、抗干扰更强,但对差分布线与端接更敏感。

二、为什么LVDS更适合“工业抗干扰”

工业现场最常见的敌人是:长线束、地电位差、开关电源纹波、变频器、电机启停的共模干扰、静电放电。RGB与LVDS在电气层面的差异,决定了它们面对这些问题时的“底子”。

1、LVDS的典型电压摆幅与共模

以TI的LVDS器件描述为例,常见LVDS输出差分摆幅是约350mV(100Ω负载),共模输出电压典型在1.2V附近。TI多份资料都提到LVDS驱动器典型共模1.2V、差分摆幅350mV。

同时,LVDS标准一致性指标中,器件说明也给出符合TIA/EIA-644的最低差分输出电压量级(例如最小247mV)等信息。

这意味着LVDS是“低摆幅+电流驱动+差分”的组合:对外辐射更小,对共模噪声更不敏感,且在地电位差存在时更有容忍度(不少器件会在规格里说明可承受一定的地电位差)。

2、RGB并行接口的典型特征

RGB并行接口的信号(数据线、时钟、同步)通常是单端CMOS/TTL电平。它靠像素时钟边沿去采样并行数据,线多且彼此紧密相关:任何一根线的串扰、过冲、地弹、时序偏斜,都可能在屏上表现为抖动、闪点、偶发花屏或边缘噪点。由于它不是差分结构,对地参考与回流路径更敏感,线束一长、环境一吵,就更难控。

在工业设备中,这个差异会直接转化为:

1·RGB更容易在EMI整改里“被动挨打”(要靠屏蔽、地设计、走线等慢慢补)

2·LVDS更像“先天抗性更强”(但也要做到差分对阻抗、端接、走线规则)

三、带宽与可用分辨率

RGB与LVDS谁更能扛“高分辨率/高刷新”,这里要先纠正一个常见误解:很多人以为“RGB是并行的,所以一定更快”。工程上并不总是这样,因为速度瓶颈往往不在“单根线快不快”,而在线数、走线匹配、连接器与线束可实现性。

1、RGB:每个像素周期并行吐出一个像素

NXP关于RGB并行接口的说明提到:并行数据接口“1个时钟周期需要24位(或其他格式)表示1个像素”。

也就是说,RGB接口的“带宽”主要取决于你能跑多高的像素时钟,以及你的板级/线束能否保证这些线在该频率下满足时序裕量。

优点:协议简单、直观;

代价:线数暴涨,时序收敛困难,越高像素时钟越难做可靠。

2、LVDS:序列化后走差分对

面板常用的LVDS链路(如FPD-Link/OpenLDI类)把24位RGB等信号序列化后输出,典型是4D+C。

序列化的好处是:线更少,且差分传输更适合高速与更长连接;因此它在大量中尺寸工业液晶屏上成为主流接口之一。

TI的某些FPD-Link序列化器资料还会给出吞吐指标。

对工业应用而言,这类来源能帮助你在官网解释:“为什么同样分辨率,LVDS更容易实现稳定传输”。

四、线束与连接器

1、RGB的线数:

数据线+时序线,少则二十多根,多则三十多根以常见24位RGB为例:

1·数据线:R/G/B共24根

2·时序:PIXCLK、HSYNC、VSYNC、DE(以及可能的复位、背光控制等)

NXP应用笔记中展示的示例接口用到18位RGB数据线(DISPB_DATA[17:0])以及HSYNC、VSYNC、DE、PIXCLK。

如果你做24位,就更“粗壮”。这直接带来:更宽的FPC/FFC、更多针脚连接器、更复杂的线束、更多回流与串扰处理工作。

2、LVDS的线数:

差分对为单位,常见4D+C(5对)或更少/更多(取决于位宽与链路)TIFPD-Link文档明确给出4data+clock(4D+C)的典型结构。

对比RGB的二三十根单端线,LVDS往往在连接器、排线宽度、线束装配一致性上更有优势。

工业项目的现实经验是:

1·线越多,装配出错率越高,批量一致性越难控

2·线越少、差分越规范,工艺窗口越大

五、为什么很多工业液晶模组“越到现场越像玄学”

1、LVDS的EMI优势有明确来源依据

TI关于LVDS技术的概述提到:由于信号摆幅更小,LVDS相较传统CMOS/TTL等能减少EMI影响,原因包括电流模式驱动、软转换、低开关电流和真正的差分传输。

TI在FPD-Link介绍中也提到LVDS在EMI方面相较其他技术有优势,强调其较低的谱内容(EMI)。

2、RGB的EMI挑战:

RGB并行接口的像素时钟会带着大量高频能量,数据线同时翻转会形成较大的瞬时电流与回流压力。线束一长,等效成“天线”,很容易引入辐射/传导问题,现场与实验室差异也会变大(现场地线、机壳接地、线束走向更不可控)。

因此很多工业项目最终的选择逻辑会变成:

1·若是板对板、距离很短、结构紧凑,RGB仍然可控

2·若存在跨板连接、线束绕行、干扰源丰富,LVDS往往更稳

六、布线与调试难度:

RGB难在“时序一致”,LVDS难在“差分链路规范”

1、RGB:你要对每一根线负责

RGB并行口的核心难点是时序:像素时钟到来时,数据必须在建立/保持时间窗口内稳定。线多意味着:

每根线的长度差带来偏斜

串扰带来波形畸变

回流路径不佳带来地弹

如果再叠加“屏端TCON对时序要求比较紧”,你会在调试阶段花大量时间在波形与时序裕量上。

2、LVDS:对差分对、端接与阻抗负责

LVDS常用100Ω差分端接,差分对要匹配长度与阻抗,走线需要控制耦合、过孔与参考平面完整。好处是通道少,规则清晰;难点是高速差分不允许“随便画”,连接器、FFC、转接板都可能成为瓶颈。

从工程管理角度看:

RGB是“线太多,问题太分散”

LVDS是“线少但每条都要按规范来”

七、可靠性与维护

1、可替换性:接口决定你能否“换屏不换板”

很多LCD液晶屏型号会在生命周期里更新。RGB接口对面板时序参数敏感(行场、极性、像素时钟、DE模式等),换屏往往意味着重新核对一套时序;LVDS面板也同样需要匹配映射与时序,但行业里LVDS面板生态更成熟,很多替代料遵循相近链路规范,系统的适配空间相对更大(前提是你预留了驱动与映射的弹性)。

2、抗环境:震动、粉尘、氧化、松动

线束越多、针脚越多,长期震动与氧化带来的接触风险越大。LVDS用更少的差分对,连接器针脚数更小,在“装配一致性”上通常更占优。

八、把“接口选型”变成可落地的决策

下面给出一套工业项目里非常实用的选择逻辑,你可以直接写进官网“选型指南”,也适合业务同事拿去沟通客户。

1、优先考虑RGB的典型场景

1·主板与液晶模组距离极短(板对板/短FPC),结构紧凑

2·分辨率不高或像素时钟可控,且对EMI约束没那么苛刻

3·主控自带成熟RGB/LTDC接口,软件栈与团队经验更偏RGB

4·希望链路简单直观,调试资源(示波器、逻辑分析)足够

RGB接口的信号组成与时序在NXP、ST等主控文档中都有明确描述,适合做标准化配置与验证。

2、优先考虑LVDS的典型场景

1·需要跨板连接、线束更长、环境干扰更强

2·需要更好的EMI表现,减少整改成本

3·分辨率与刷新提升后,RGB的并行线束与时序收敛成本过高

4·产品要做更强的批量一致性与可维护性

LVDS在电气摆幅与EMI方面的优势有明确技术依据(低摆幅差分),面板链路(如FPD-Link)对24位RGB常见4D+C结构也有清晰的行业实现。

3、接口选择要和结构形态绑定

很多项目不是因为“接口理论上不行”失败,而是因为结构让它变得不可控:

1·想用RGB,但屏在门板上、主板在机箱里,中间一根长排线绕来绕去

2·想用LVDS,但转接板太多、连接器没选对、差分对被迫绕线且参考地不连续

接口选型时,把“线束长度、走线路径、连接器形态、接地方案”一起写进评审,往往能少走一半弯路。

九、建议做这些测试

为了让“选型”变成可验证的结论,而不是主观判断,建议你建立接口验证清单:

1·信号完整性:关键边沿、过冲/欠冲、抖动、差分眼图(LVDS)

2·EMI预评估:整机在典型工作模式下的辐射/传导趋势

3·温度与老化:高低温下花屏/闪烁概率、连接器接触稳定性

4·抗扰度:电机启停、继电器吸合、ESD点放对画面影响

5·批量一致性:至少三套样机/小批试产复现概率

尤其在工业场景,“稳定性”是第一指标,参数再漂亮,现场不稳就是返工成本。

十、常见问题

Q1:RGB接口不是并行的吗,为什么反而更容易出问题?

并行本身不等于容易。RGB需要二三十根单端线在同一像素节拍下协同工作,任何一根线的偏斜、串扰、回流不良都可能破坏采样窗口。它的难点在“线太多、时序太紧”,尤其当线束变长、环境变吵时更明显。

Q2:LVDS为什么更适合工业抗干扰?有数据依据吗?

LVDS典型差分摆幅约350mV、共模约1.2V,属于低摆幅差分传输。相关技术资料指出,小摆幅与差分传输可降低EMI,并减少对共模干扰的敏感度。

Q3:面板说“LVDS接口”,就是TIA/EIA-644标准吗?

电气层面往往遵循LVDS(TIA/EIA-644/644A)一类标准的摆幅与阈值要求;但在显示行业,“LVDS屏”常常还包含特定的面板链路格式(例如FPD-Link/OpenLDI映射)。因此选型时既要确认电气兼容,也要确认通道数、位宽映射与时序。

Q4:LVDS是不是就一定能走很长线?能走多远?

标准本身不直接给出统一的“米数”,距离取决于数据速率、线缆类型、端接、损耗与EMI环境。工程上LVDS通常比并行RGB更适合跨板和更长连接,但要按差分链路规范做线材与端接,并在目标线长上做实测验证。

Q5:我已经选了RGB屏,后期发现EMI难控,还有补救空间吗?

有,但成本会逐步上升。常见思路包括:缩短RGB线束、加强地参考与回流、优化走线与串扰、增加屏蔽与滤波、降低像素时钟或刷新策略、结构上调整线束路径。若结构允许,评估把并行RGB转换为LVDS再走线,也是一条常见的工程路线(需要额外的序列化/反序列化器件)。

最新资讯

- 2026-02-10 15.6寸LCD工业液晶屏1000高亮度屏功

- 2026-02-06 LCD10.1寸工业液晶屏常见问题:分

- 2026-02-05 精显科技2026年春节假期安排通知

- 2026-02-05 8寸工控LCD液晶屏尺寸一样但孔位

- 2026-02-04 TFT-LCD工业液晶屏型号后缀怎么看

- 2026-02-03 京瓷TCG057VGLGC-G50-S带触摸一体液晶

- 2026-02-02 LCD液晶屏触摸屏盖板玻璃如何选?

- 2026-01-30 LCD工业液晶屏G104系列怎么选?G104S

- 2026-01-29 LCD工业液晶屏显示器花屏/闪屏/白

- 2026-01-28 15.6寸LCD工业液晶屏:常见接口是eD